3

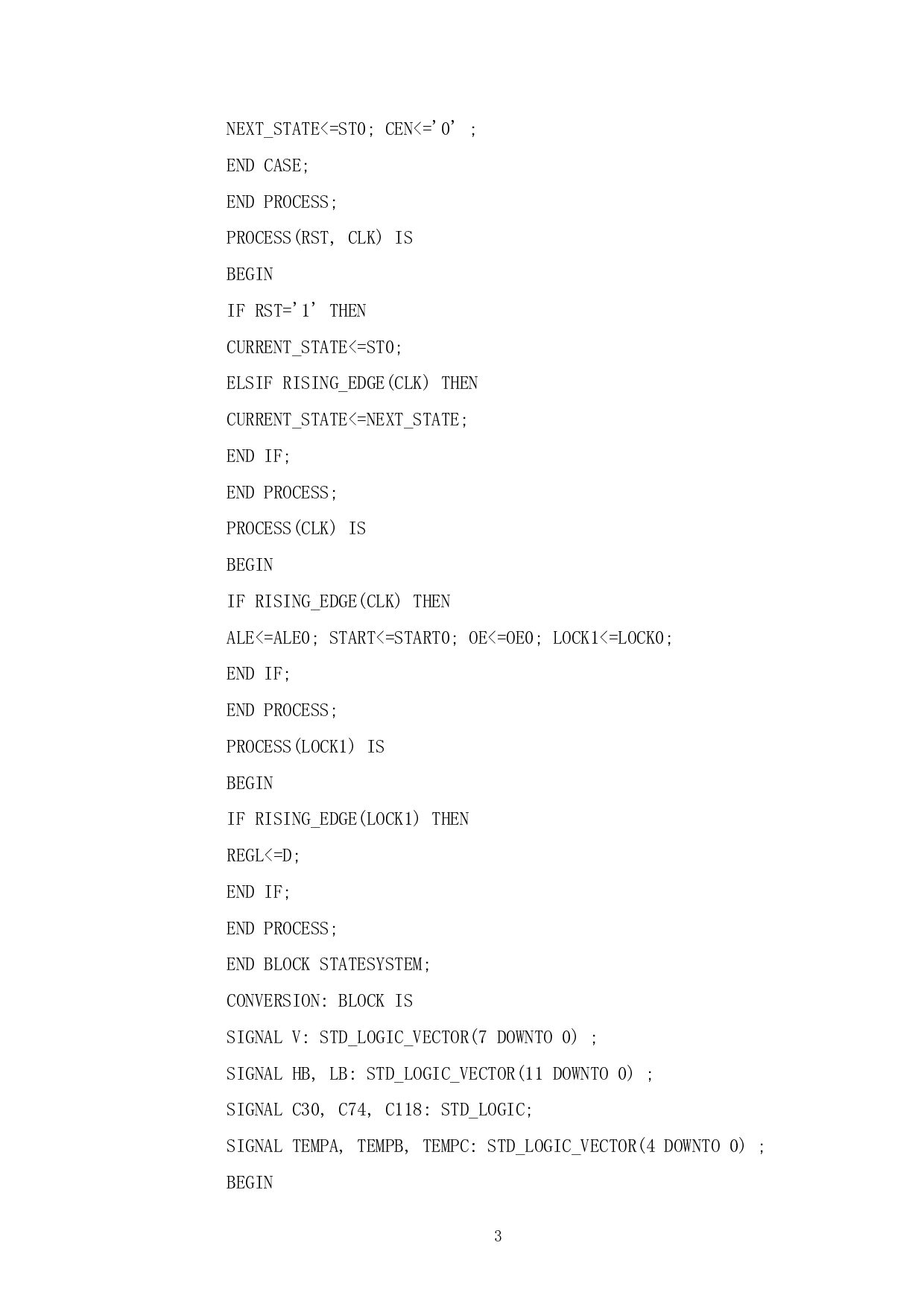

NEXT_STATE<=ST0;CEN<='0';

ENDCASE;

ENDPROCESS;

PROCESS(RST,CLK)IS

BEGIN

IFRST='1'THEN

CURRENT_STATE<=ST0;

ELSIFRISING_EDGE(CLK)THEN

CURRENT_STATE<=NEXT_STATE;

ENDIF;

ENDPROCESS;

PROCESS(CLK)IS

BEGIN

IFRISING_EDGE(CLK)THEN

ALE<=ALE0;START<=START0;OE<=OE0;LOCK1<=LOCK0;

ENDIF;

ENDPROCESS;

PROCESS(LOCK1)IS

BEGIN

IFRISING_EDGE(LOCK1)THEN

REGL<=D;

ENDIF;

ENDPROCESS;

ENDBLOCKSTATESYSTEM;

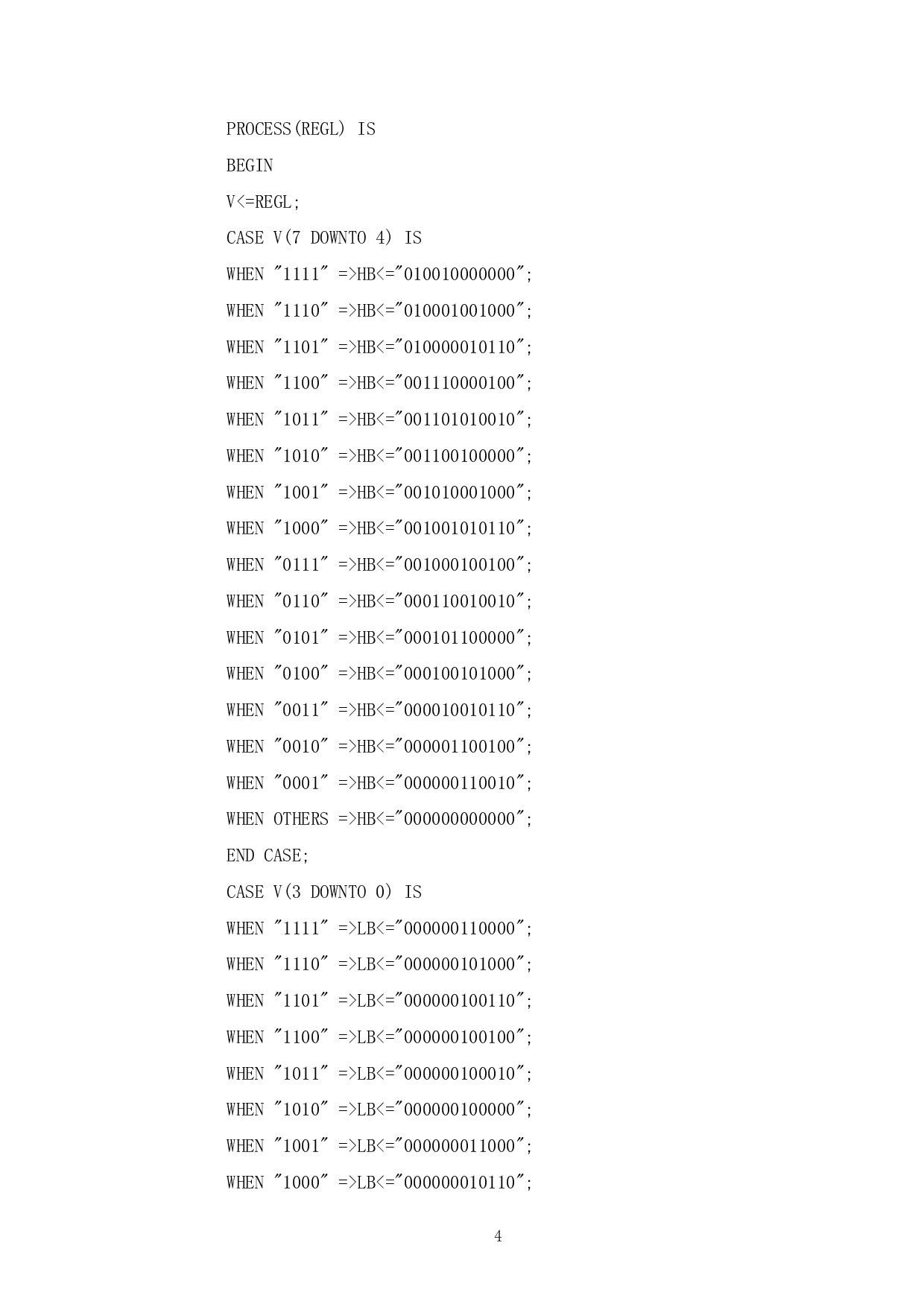

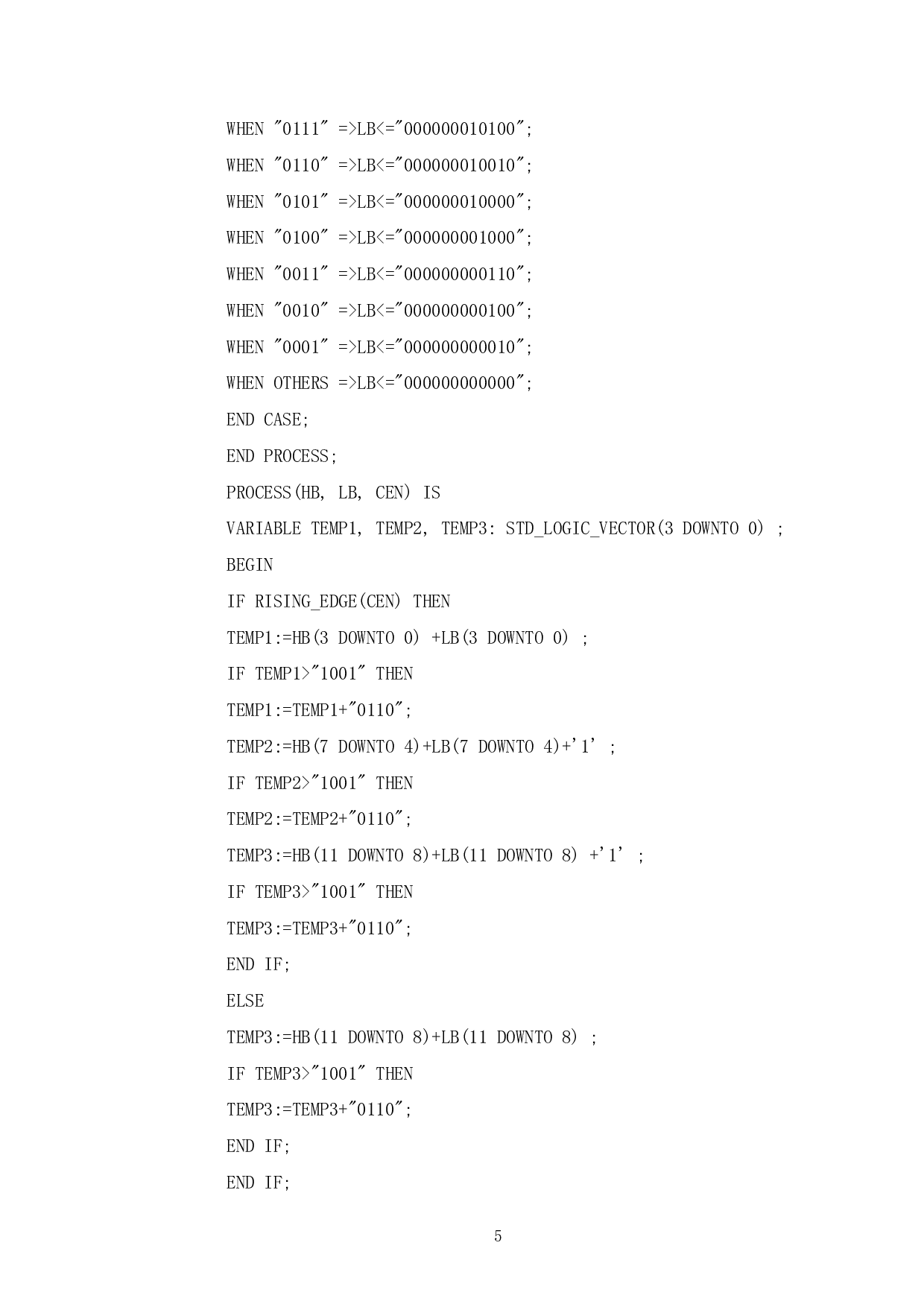

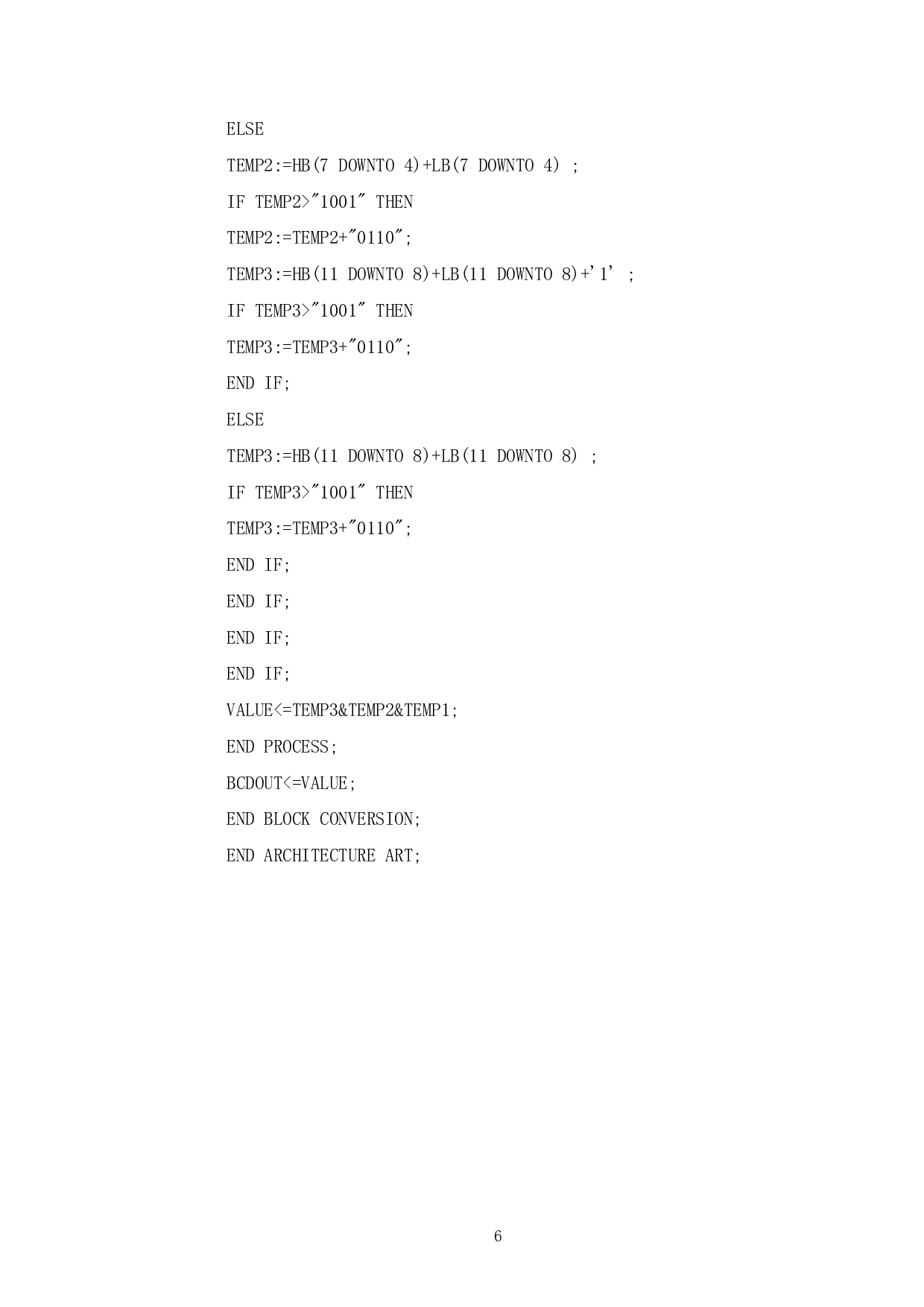

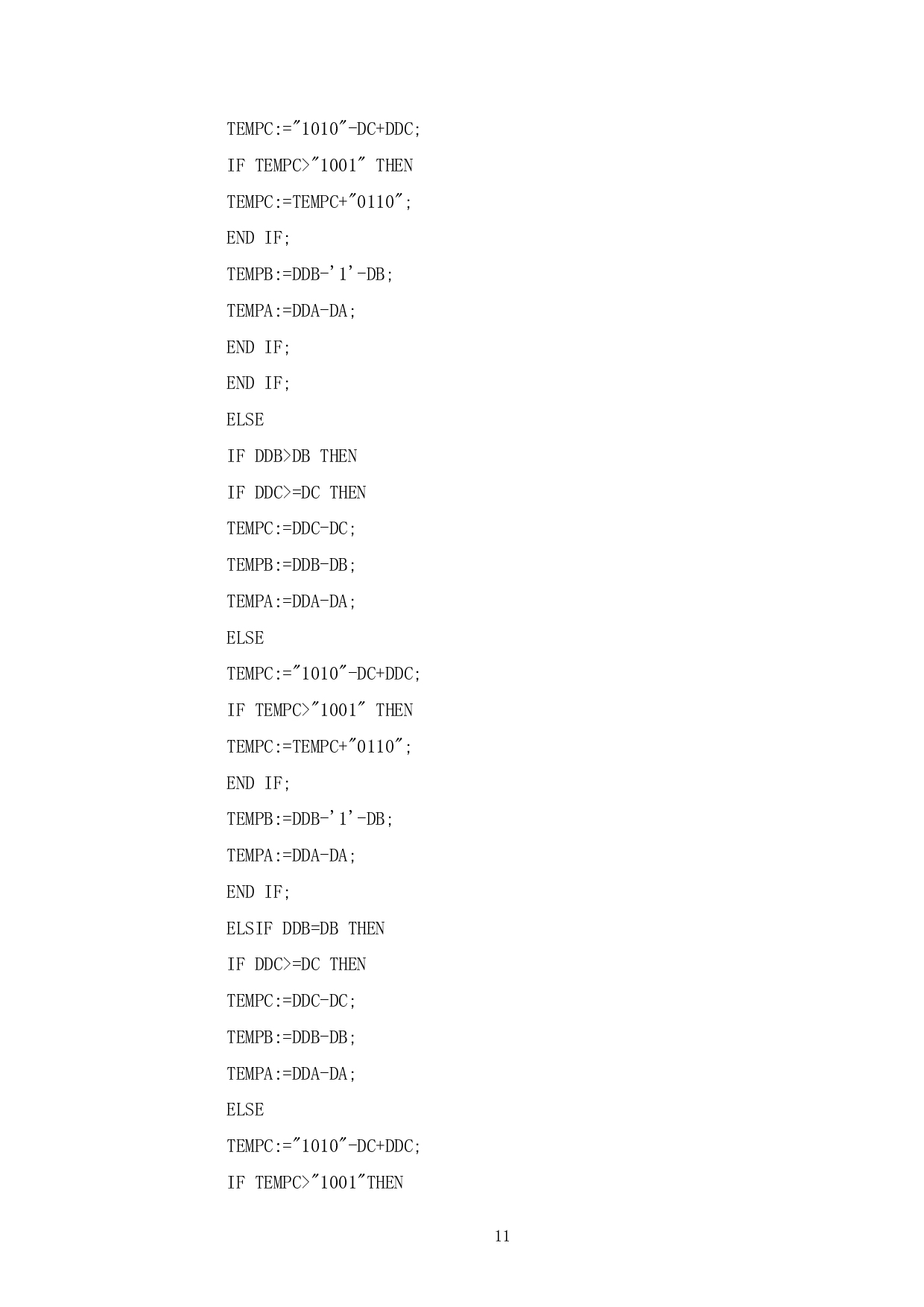

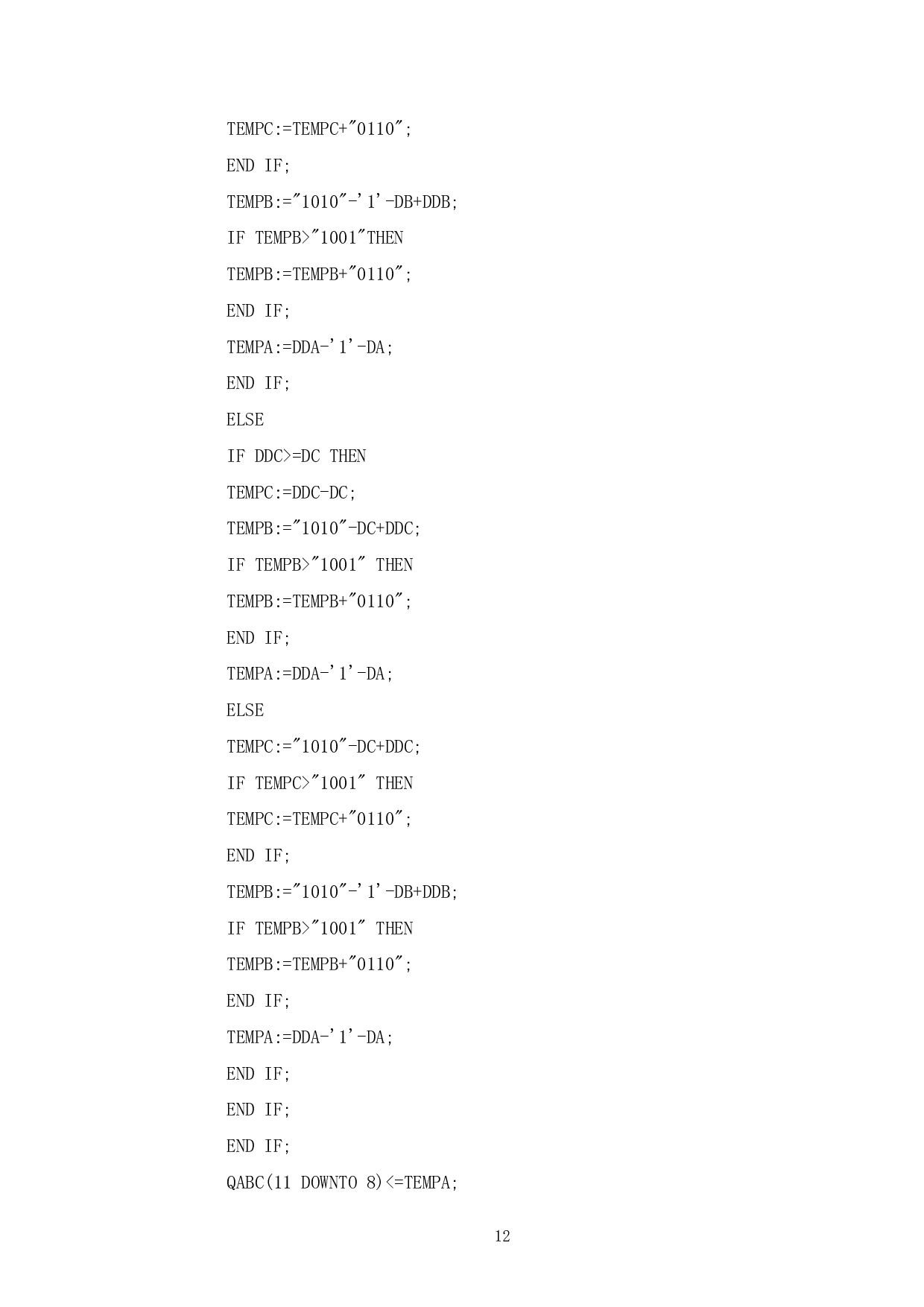

CONVERSION:BLOCKIS

SIGNALV:STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALHB,LB:STD_LOGIC_VECTOR(11DOWNTO0);

SIGNALC30,C74,C118

附录1(AD控制模块)-1224字.pdf