S

o

C

芯片封装完好性检测系统设计

摘

要

S

o

C

芯片封装的完好性检测系统,

可以

在不经过

ATE

测试机等专用设备的情况下进行芯片管脚的开短路测试,这个检测系统大大降低测试的成本以及提高测试的便捷性。

测试系统

对芯片进行开短路测试时会采用加电流测电压(

FIMV

)或者

采用

加电压测电流(

FVMI

)的方法

。测试系统

采用串行的连接方式测试芯片管脚,测试模式由多路复用开关进行切换。芯片管脚的输入电压和输入电流由

MCU

控制,

同时测试电路

对输出的电流和电压进行采集

,并且

电流和电压

返回到

MCU

进行

比较,

通过比较

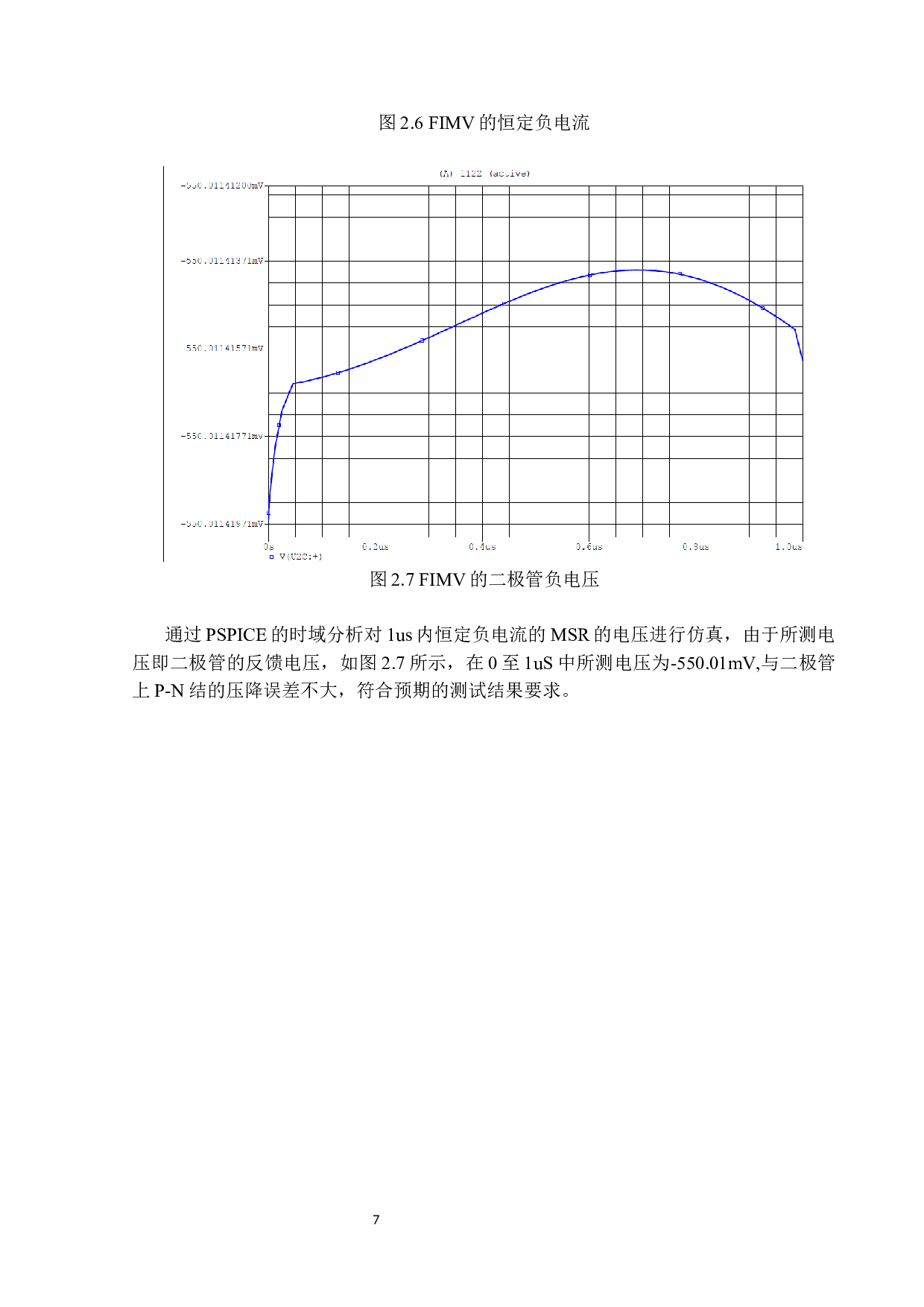

SoC芯片封装完好性检测系统设计-10761字.docx