Abstract

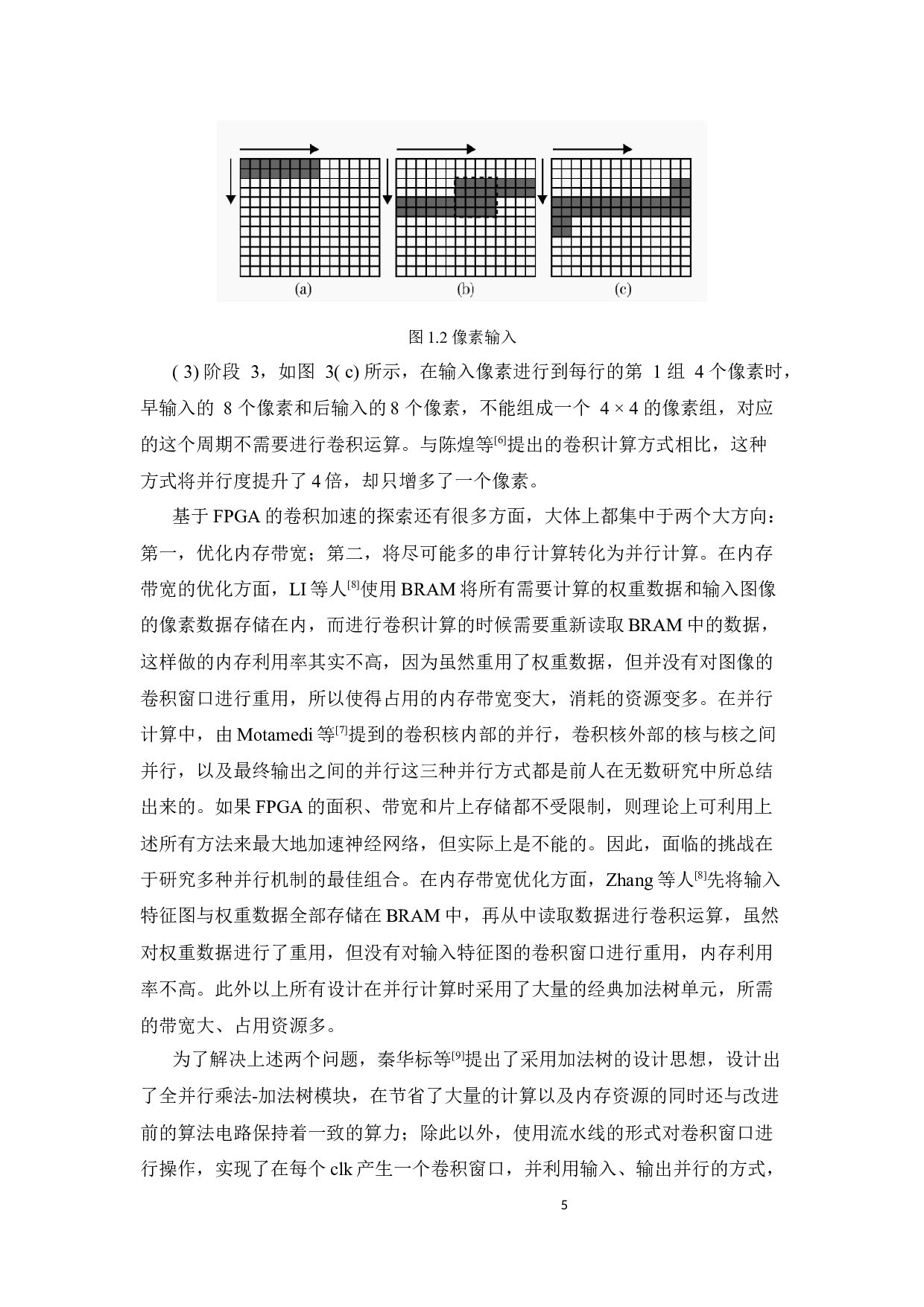

The rise of artificial intelligence is inseparable from the development of deep neural network, The progress of neural network depends on the improvement of computing power of AI processor. The efficiency of convolution calculation often plays an important role. Therefore, the research on the circuit design of convolution acceleration is crucial for the research and development of AI chips.

Based on Xilinx's FPGA development environment, we are going to analyze and discuss the convoluti

基于Verilog的数字卷积器设计-16435字.docx